CMOS Testing: Part 1 • Introduction • Fault models – Stuck-line (single and multiple) – Bridging – Stuck-open • Test pattern generation – Combinational circuit test generation – Sequential circuit test generation

Lecture 19: CMOS Testing – Sanjay Vidhyadharan

Pre-fabrication Testing / Logic Verification, Corner Analysis, Design for Testability, Observability & Controllability, Stuck-At Faults, SSL Fault Detection, Multiple Stuck-Line (MSF) Faults, Test Pattern Generation, Bridging Faults, Stuck-Open Faults, Sequential Circuit Test Generation, AdHoc Design for Testability, Scan-Path Design, Static ...

Basics of testing CMOS - Test and Measurement tips

2018年3月16日 · The testing of CMOS circuits is a complex subject that goes far beyond what a single article can cover. Nevertheless, many of the more sophisticated testing schemes rely on a few basic concepts. To understand the basics, it helps …

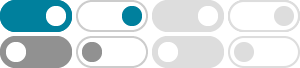

Design for Test • Design the chip to increase observability and controllability • If each register could be observed and controlled, test problem reduces to testing combinational logic between registers. • Better yet, logic blocks could enter test mode where they generate test patterns and report the results automatically.

Built-in Self-test (BIST) Advantages •Lower cost due to elimination of external tester • In-system, at-system, high-quality testing • Faster fault detection, ease of diagnosis • Overcomes pin limitations and related interfacing problems • Reduces maintenance and repair costs at system level Issues Test strategy (random, exhaustive ...

Basics of testing CMOS - Electrical Engineering News and Products

2018年3月16日 · To understand the basics, it helps to first review how a CMOS device operates. A single CMOS device consists of two FETs, one P-type and the other N-type, arranged in a symmetrical configuration. The data input is typically applied to the gates and an inverted output extracted from the connected drains. Bias is applied to the sources.

In CMOS Test and Evaluation: A Physical Perspective, we have attempted to describe the relationship between basic circuit components (resistors, capacitors and diodes, and MOSFETs) and a complex CMOS chip with as many as several billion transistors. Our approach is to provide an overview with examples to

Electrical Tests and Characterization in Manufacturing

2014年1月1日 · This chapter focuses on test methods for digital CMOS circuits and characterization techniques to bring together the learning from CMOS circuit components, on-chip monitors, and functional tests. An introduction to parametric, structural, and functional testing of CMOS chips along with DFT features is given in Sect. 7.1 .

Test structures are used for a variety of purposes in the fabrication of integrated circuits. Test structures are used for device, circuit and process parameter extraction, as well as random fault

CMOS Test and Evaluation: A Physical Perspective - Springer

CMOS Test and Evaluation: A Physical Perspective is a single source for an integrated view of test and data analysis methodology for CMOS products, covering circuit sensitivities to MOSFET characteristics, impact of silicon technology process variability, applications of embedded test structures and sensors, product yield, and reliability over ...

- 某些结果已被删除